I am currently a member of the VLSI Design and Test Lab at SDSU where I design digital circuits targeting FPGA and ASIC platforms. My PhD co-advisors are Professor Amir Alimohammad (SDSU) and Professor Patrick Mercier (UCSD).

My research focuses on the implementation of brain-computer interfaces (BCIs), particularly how we can design scalable wireless BCIs for future implantable use. I study a variety of topics, ranging from digital circuit design to machine-learning based neural decoding. I've also had the pleasure of being the teaching assistant for various digital logic courses at SDSU throughout my studies.

My hobbies include hiking, playing board and card games, listening to jazz, and making/drinking coffee ☕.

Recent Publications

In this article, we investigate the feasability of employing low-frequency local field potentials (LFPs) to realize efficient low-power brain-switches. Our findings suggest that LFPs may contain sufficient information to realize brain switches without requiring complex pre-processing such as channel selection or filtering requirements. Compared to our previous spike-based realization of brain-switches, the LFP-based brain switch consumes over 97% less power while achieving comparable user intention performance.

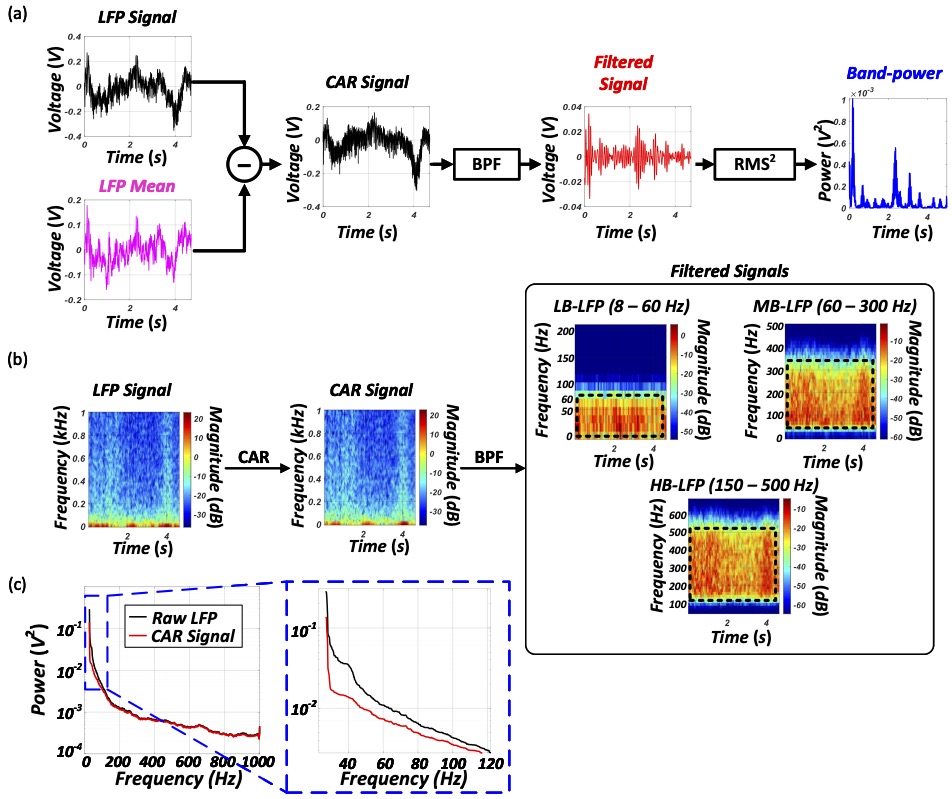

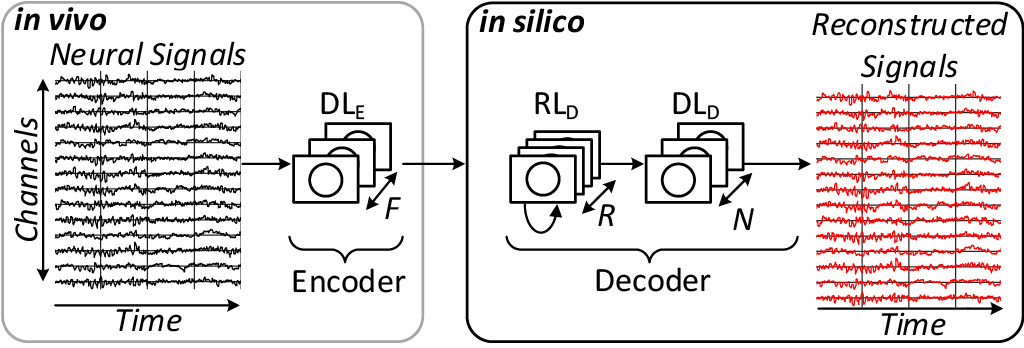

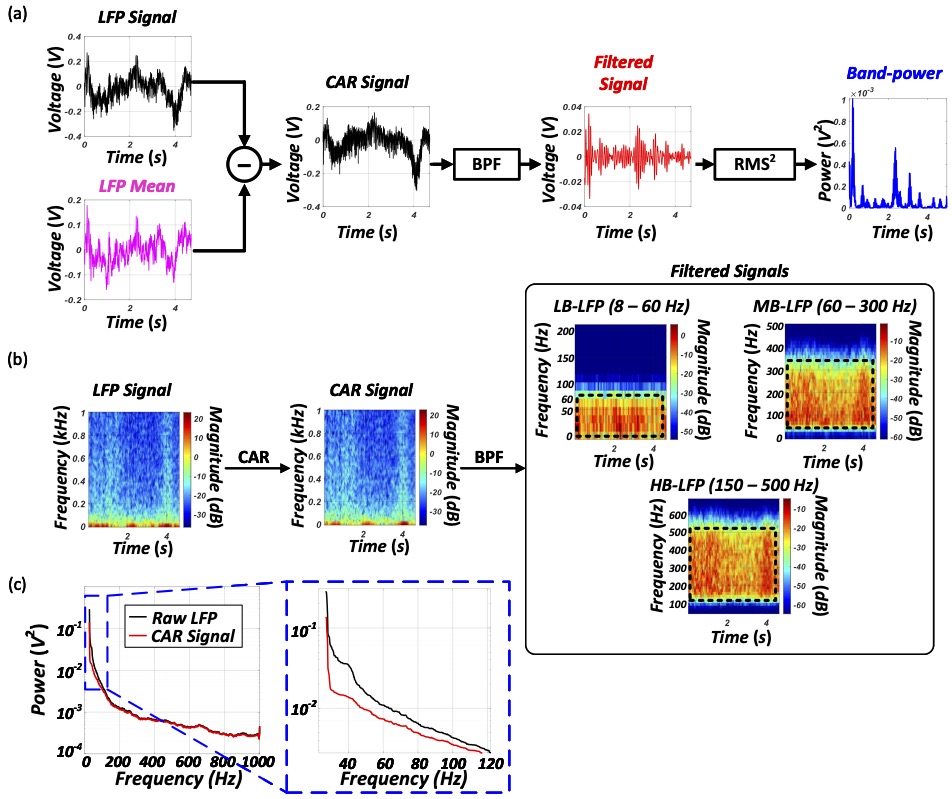

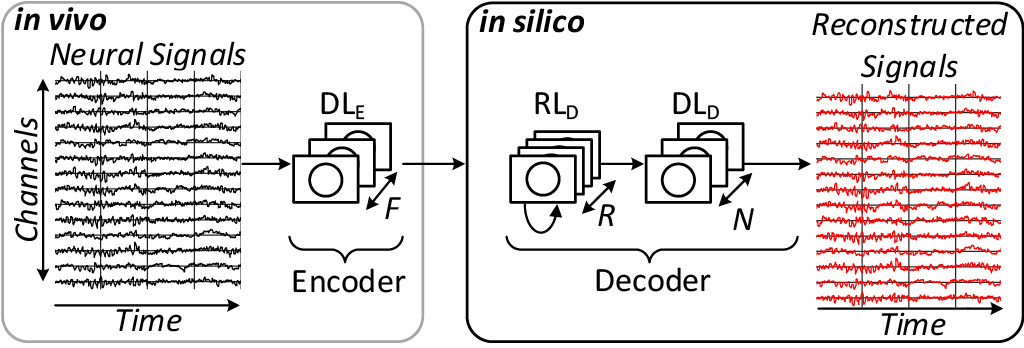

In this article, we present the design and implementation of a signal compression autoencoder-based neural network for reducing the large data rate of intra-cortical recording arrays when targeting local field potentials. We employ various architectural and signal optimizations to reduce the computational complexity and memory requirements of the in vivo encoder sub-network.

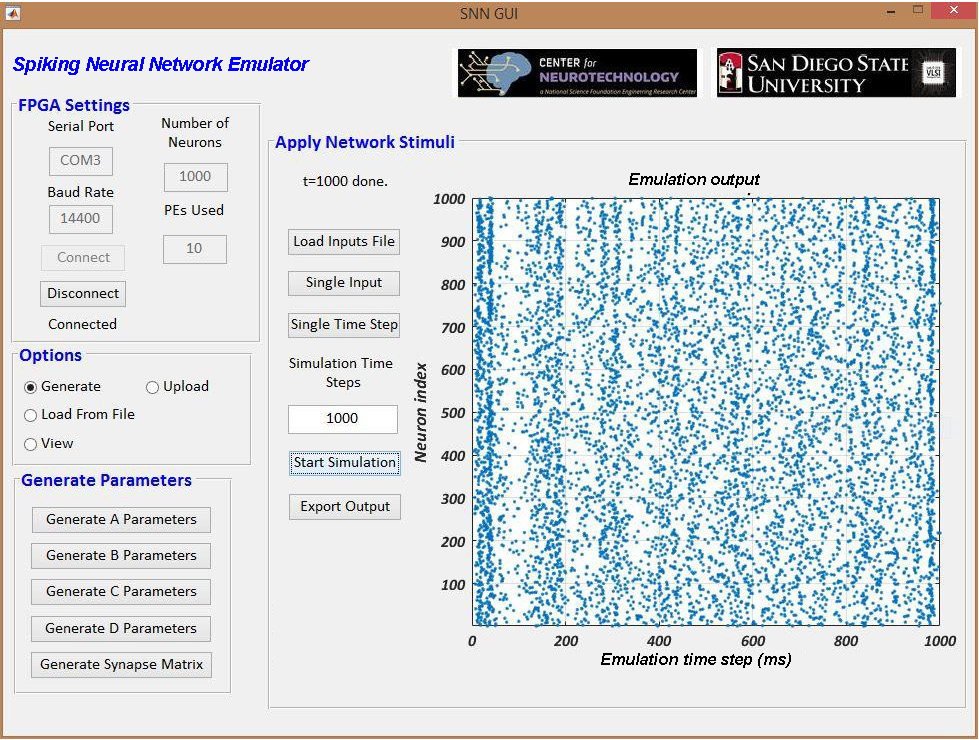

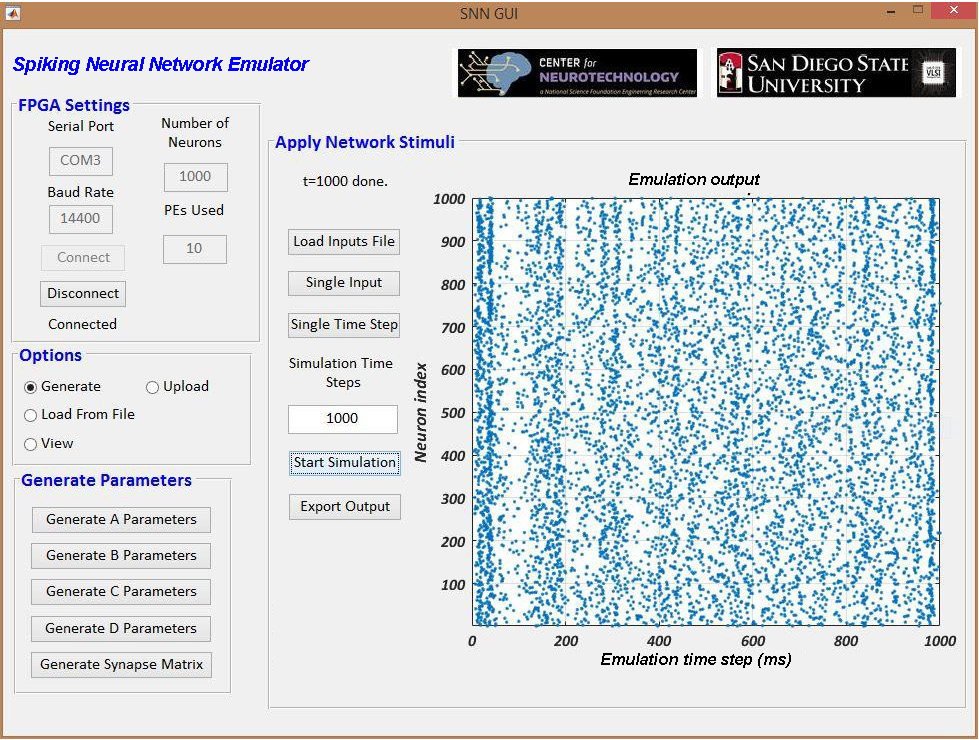

In this article, we detail the design and architecture of a generalized hardware architecture to emulate spiking neural networks on FPGAs.

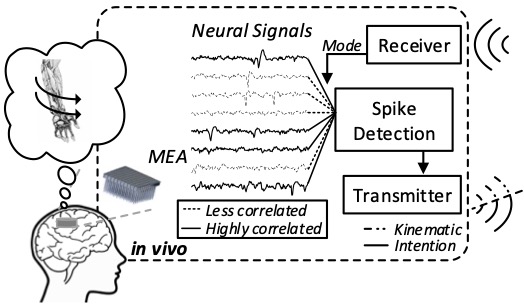

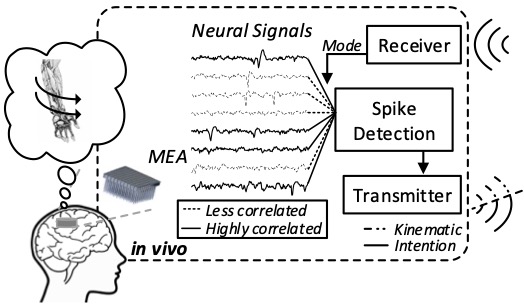

In this article, we present the first practical realization of a brain-state estimation brain-machine interface (BMI) for reducing the power and energy consumption of in-vivo neural recording circuitry. Neural spike detection is performed on a small subset of channels to realize an asynchronous BMI in which the user can initiate a BMI task at their leisure rather than specific times. During inactive or resting states, the neural signal processing is reduced to save considerably power and energy of the in-vivo signal processing circuitry.